Семейство Radeon R4. XX: Справочная информация о семействе видеокарт Radeon XСправочная информация о семействе видеокарт Radeon X1. Справочная информация о семействе видеокарт Radeon HD 2.

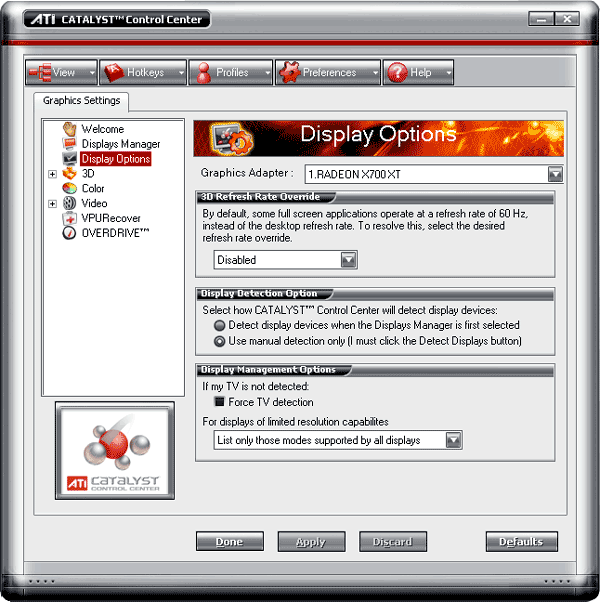

ATI Radeon X800 XT Platinum Edition В наши руки попал. ATI Radeon X700 Pro Не очень. А теперь распишем всю схему подключения аппаратуры. Семейства видеокарт AMD(ATI) RADEON Справочная информация. Технология 130 нм (TMSC, low-k, медные соединения); 160 миллионов транзисторов; FС корпус. Пытливый читатель сразу отметит, что схема практически совпадает с NV40. Решил снять видео по ремонту видеокарт. В данном случае на операционном столе находится видеокарта ATI Radeon 7770, которую . Схема для 7-ми контактного разъёма приведена для карт RADEON. Такие разъёмы имеются далеко не у каждого телевизора. Подробные характеристики видеокарты GIGABYTE Radeon X700 Pro 420Mhz PCI-E 128Mb 864Mhz 128 bit DVI TV YPrPb, отзывы покупателей, обзоры и . В связи с тем, что для каждого чипа схема включения полностью индивидуальна, апгрейд видеокарты в 70% не возможен. Radeon X700 на данный момент является mainstream решением в линейке Sapphire. В графическом процессоре RV410, устанавливаемом на эту карту, .

Справочная информация о семействе видеокарт Radeon HD 4. Справочная информация о семействе видеокарт Radeon HD 5. Soulful House Торрент подробнее. Справочная информация о семействе видеокарт Radeon HD 6. Справочная информация о семействе видеокарт Radeon HD 7.

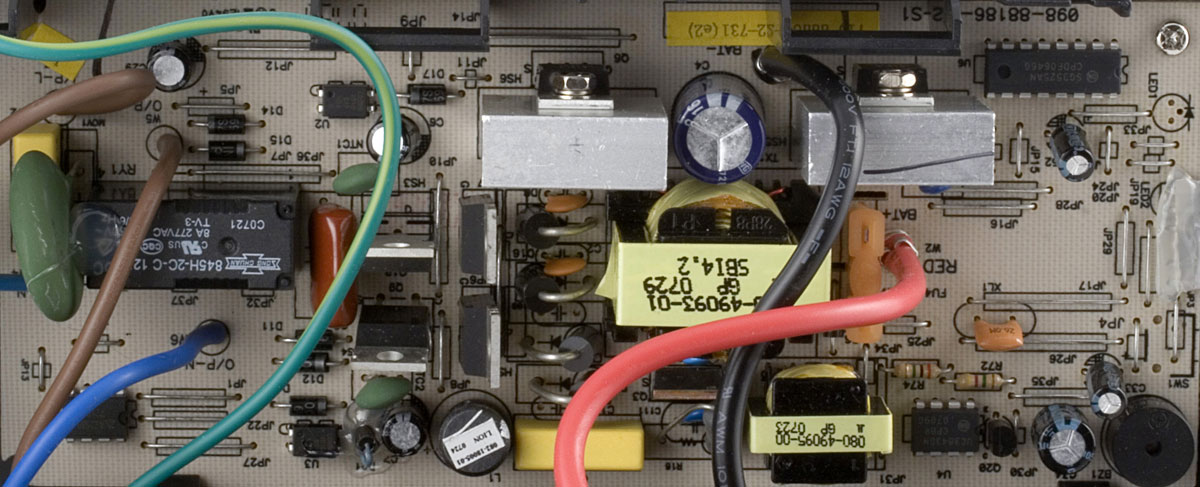

Востанавливаем Radeon 9600 Pro: память вышла из строя · Выгорела Radeon 9600XT. Помогите найти схему для блока питания floston · Помогите с . Семейство ATI Radeon X700. ATI Radeon X700 Pro — конкурент NVIDIA GeForce 6600, а конкурентом видеокарты. Структурная схема чипа R520.

Справочная информация о семействе видеокарт Radeon 2. Справочная информация о семействе видеокарт Radeon 3. Спецификации чипов семейства R.

Сжатие буфера кадра и буфера глубины в MSAA режимах. Возможность менять MSAA паттерны от кадра к кадру (Temporal AA)Анизотропная фильтрация степени до 1. Все необходимое для поддержки пиксельных и вершинных шейдеров версии 2.

Дополнительные возможности пиксельных шейдеров на основе расширенной версии 2. Дополнительные возможности вершинных шейдеров, сверх базовых 2. Новая техника сжатия текстур, оптимизированная для сжатия двухкомпонентных карт нормалей (т. Dc, степень сжатия 4: 1)Поддерживается рендеринг в буфера плавающего формата, с точностью FP1.

FP3. 2 на компоненту, возможность блендинга отсутствует. Поддерживаются трехмерные и FP (плавающие) форматы текстур, без текстурной фильтрации. Поддержка «двустороннего» буфера шаблонов.

MRT (Multiple Render Targets — рендеринг в несколько буферов)2 x RAMDAC 4. МГц 2 x DVI интерфейса TV- Out и TV- In интерфейс (требуются интерфейсные чипы)Возможность программируемой обработки видео - пиксельные процессоры задействуются для обработки видео потока (задачи компрессии, декомпрессии и постобработки)2.

D ускоритель с поддержкой всех функций GDI+Общая схема чипа R4. Пытливый читатель сразу отметит, что схема практически совпадает с NV4. Ничего удивительного - обе фирмы стараются создать оптимальное решение и уже несколько поколений исповедуют проверенную и эффективную организацию общей структуры графического конвейера. Существенные отличия кроются внутри блоков и в первую очередь - в пиксельных и вершинных процессорах.

Скорее всего, в отличие от NV4. В наличии четыре независимых процессора квадов, каждый из которых может быть отключен - таким образом, в зависимости от потребностей рынка и наличия бракованных чипов можно отключать один, два или даже три процессора, производя, таким образом карты, обрабатывающие 4, 8, 1. Заявлено, что R4.

Вершинные блоки не соответствуют ни полной спецификации vs 3. NVIDIA (т. н. Что касается арифметической производительности, то за один такт вершинный процессор R4. FP3. 2) и одну скалярную FP3. NV4. 0. Напомним, что R3.

XX во многом проигрывал чипам NVIDIA из- за отсутствия специальных аппаратных блоков расчета освещения, ускорявших эмуляцию T& L вот уже в трех поколениях чипов NVIDIA. Пиксельные процессоры и организация закраски Рассмотрим пиксельную архитектуру R4. Итак, после установки параметров треугольника нас ждет: Остановимся на самых интересных фактах.

Во- первых, если ранее в R3. XX было максимум два процессора квадов, обрабатывающих за такт блок из четырех пикселей (2х. Они полностью независимы и каждый из них может исключаться из работы (например, для создания облегченной версии чипа с тремя процессорами при наличии брака в одном из них).

Итак, сначала треугольник разбивается на блоки первого уровня (8х. Z буфера. Его объем не афишируется, но, судя по всему, в R4. Всего на этой стадии может быть откинуто до 4 блоков за такт, т. Отметим, что в зависимости от режима MSAA один элемент этого буфера может соответствовать 4 (нет), 8(MSAA 2х), 1. MSAA 4х) или даже 2. MSAA) точкам в буфере кадра, вот почему его выделили в отдельную структуру, занимающую промежуточный уровень между мини буфером глубины полностью расположенном на чипе и окончательным буфером глубины базового уровня. Таким образом, в продуктах NVIDIA мы имеем дело с двухуровневой организацией HSR и буфера глубины, а в продуктах ATI - с трехуровневой.

А вот еще дальше начинаются самые существенные отличия R4. NV4. 0: Алгоритм работы пиксельного процессора NVIDIA: Цикл по командам шейдера Считать микрокод следующей команды Сконфигурировать текстурный модуль и все ALU Цикл по всем квадам в очереди Прогнать квад через процессор, TMU и ALU Конец цикла по квадам Конец цикла по командам шейдера. Алгоритм работы пиксельного процессора ATIЦикл по 4 фазам Цикл по все квадам в очереди Цикл по выбираемым текстурам в этой фазе (до 8) Выбрать значение текстуры Конец цикла по текстурам Цикл по вычислительным командам в этой фазе (до 1. Конец цикла Конец цикла по квадам Конец цикла по 4 фазам. Итак, NVIDIA постепенно исполняет команды (а точнее суперскалярные пачки команд, включая команды выборки текстур), прогоняя через каждую команду все квады находящиеся в обработке. ATI же разбивает шейдер на четыре фазы (вот откуда ограничение на глубину зависимых выборок не более 4), в каждой из которых сначала осуществляется выборка всех данных текстур необходимых для этой фазы, а затем уже все вычисления над полученными данными.

В том числе, и вычисление новых координат, для выборки текстур в следующей фазе. Сказать однозначно нельзя. Подход ATI хуже приспособлен к сложным шейдерам с управлением потоком команд или многочисленными зависимыми выборками. С другой стороны, вычисления внутри каждой из четырех фаз происходят по похожей на CPU схеме - выполняются все команды, команда за командой, для одного квада, затем берется следующий квад и т.

Таким образом, во время вычислений можно использовать полноценный пул из временных регистров, без какой либо потери производительности и пенальти за использование более 4 регистров, которое мы имеем в NV4. Кроме того, подход ATI требует менее длинных по числу стадий конвейеров. Следовательно, расходуется меньше транзисторов и потенциально достигаются более высокие тактовые частоты (или, что одно и то же, более высокий выход годных чипов на фиксированной частоте). Хорошо предсказуема производительность того или иного шейдера, легче писать их код, когда не надо заботиться о равномерной группировке текстурных и вычислительных команд или расходе временных регистров. Ограничение на число зависимых выборок, ограничение на число команд в одной фазе, необходимость хранить весь микрокод шейдера для четырех фаз «под рукой», т. Существует возможность задержек в случае интенсивных зависимых выборок текстур, следующих друг за другом (это сглаживается наличием набора одновременно обрабатываемых квадов, но их число не столь велико, как у NVIDIA).

Любые попытки «прикрутить» к подобной архитектуре пиксельного процессора неограниченную длину шейдеров и тем более неограниченную гибкость в текстурных выборках неизбежно вызовут множество проблем. Это ухищрение позволяет исполнять шейдеры, превышающие по длине или числу зависимых (да и обычных тоже) выборок текстур ограничения пиксельного процессора ценой дополнительных проходов, что само по себе не является бесплатным решением и далеко от идеала. По мере роста сложности шейдера число проходов и сохраняемых временно в видеопамяти данных будет возрастать, а вместе с ними будет возрастать и штраф по сравнению с архитектурами, подобными тем, что мы видим у NVIDIA, которые не ограничены длиной или сложностью шейдера.

Формат данных в процессорах при вычислениях - FP2. TMU проводятся с большей точностью. Тут все как и в R3. XX, на каждый пиксель приходится по два ALU, причем каждый из них может выполнить две различные операции по схеме 3+1 (как и в R3. XX, но там ALU был один). Подробнее об этом написано в статье DX Current.

Страницы

- Инвестиционный Договор На Реконструкцию Здания

- Уведомление Об Увольнении Образец Рк

- Типовая Должностная Инструкция Механика По Выпуску Автотранспорта

- Зарядное Устройство Жигули Инструкция По Применению

- Упражнения На Шведской Стенке

- Львів Шпалери На Робочий Стіл

- Мод Для Фарминг Симулятор 2015 Прицепы

- Кс 1.6 С Логотипом Контр Террорист

- Должностная Инструкция По Охране Труда Учителя Изо

- Сосмтавить Схему Цепи Питания Для Арктической Пустыни

- Www.Medinfo.Kz Тесты Для Медицинских Сестер На Сертификат Читат

- Кыргыз Кино Кожожаш

- Препараты Кальций Магний Инструкция